RISC-V 代码模型(2026 版)

RISC-V 指令集架构 (ISA) 在设计上兼顾简洁与模块化。为了实现上述设计目标,RISC-V 有意识地减少了寻址方式的种类,从而降低了实现复杂 ISA 时的一项重大成本。寻址方式成本高昂:在小型设计中,会增加解码开销;在大型设计中,则会引入隐式依赖成本。

来自 RISC-V 专家的最新洞察与深度技术解析

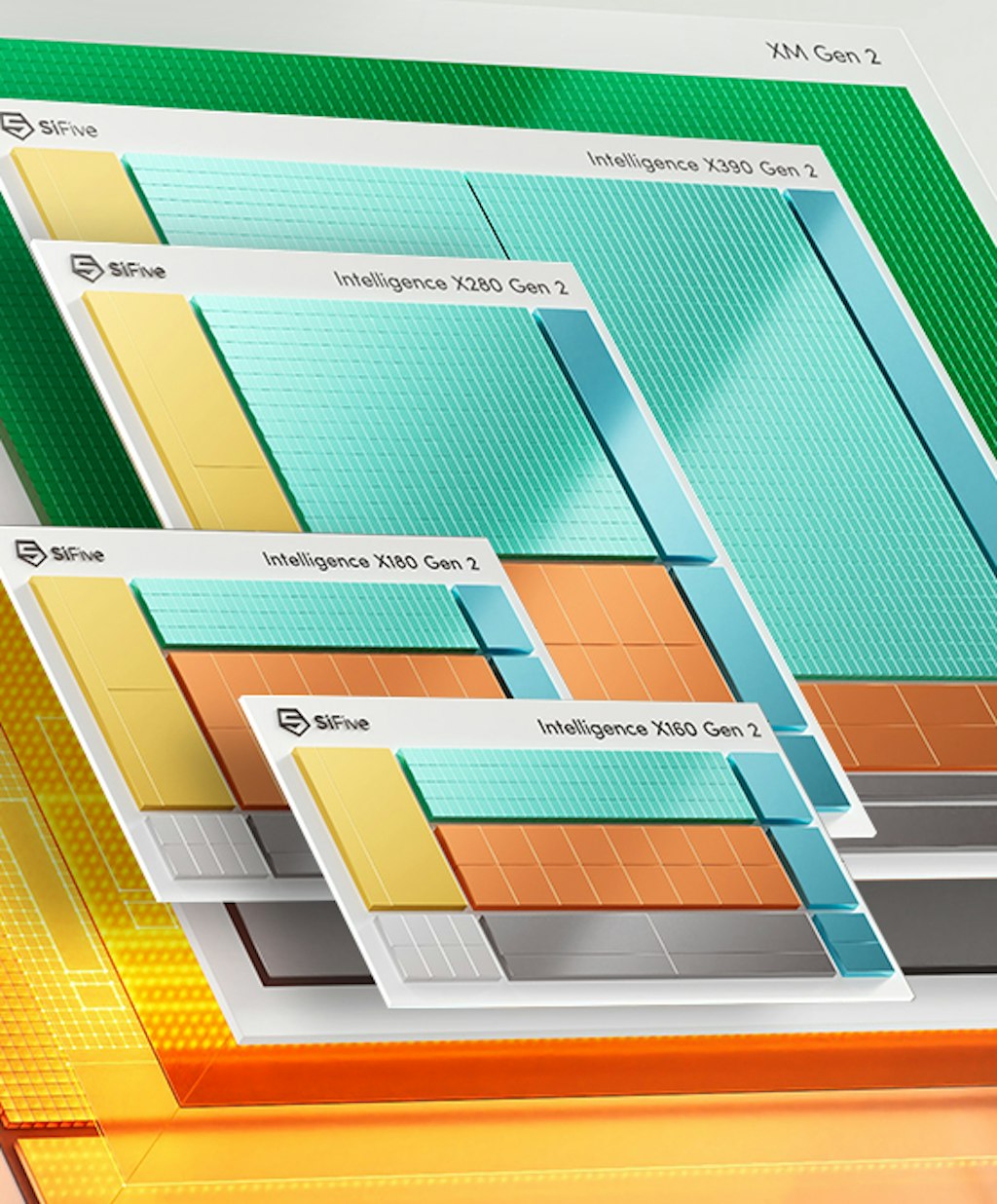

SiFive 博客是您获取 RISC-V 最新动态的首选平台,内容涵盖处理器 IP、芯片架构、软件开发及各类技术创新。无论您正在打造下一代消费电子产品、优化数据中心,还是开发新一代汽车,都欢迎关注並获取专家们的最新见解。