SiFive 博客

来自 RISC-V 专家的最新洞察与深度技术解析

Freedom Studio Version 2019.03

Ever since we launched Freedom Studio in 2017, it has been a great way to quickly and easily get started writing code for SiFive platforms, whether those platforms are development boards such as the HiFive1 Rev B, Digilent Arty FPGA, or even our testbench, which ships along with SiFive IP deliverables. Freedom Studio is based on the industry-standard Eclipse IDE and comes with several plugins and pre-built tools supporting Windows, macOS, and Linux, to help with embedded development for SiFive platforms. While the tools included in Freedom Studio have always been open-source, we have also decided to open-source our build scripts as well, which can be found in the Freedom Tools repository.

This release of Freedom Studio brings significant under-the-hood enhancements in addition to several new user-facing changes. In this blog, I will highlight several of these changes.

Freedom-E-SDK Integration

Freedom-E-SDK is a GitHub repository that contains a command-line driven workflow for targeting SiFive's embedded platforms. One of the strengths of SiFive's RISC-V Core IP is the ability to customize a certain product to meet the requirements of a specific application. A number of these configuration options can directly affect software development, such as the RISC-V ISA extensions implemented, memory map, included peripherals, and so on. In order to accommodate bare-metal software development on such a wide variation of hardware targets, we have been busy developing a new API we call Freedom Metal. Freedom-E-SDK has now been integrated with Freedom Metal and contains examples targeting the Freedom Metal API and Freedom Metal BSPs for all of our Standard Cores and development boards. Look for a future blog specifically on Freedom Metal; until then, feel free to check out the Freedom Metal documentation here.

How does this relate to Freedom Studio? Until now, Freedom Studio has contained examples that were snapshots of certain projects in Freedom-E-SDK. In the 2019.03 release of Freedom Studio, however, we now have much tighter integration between Freedom-E-SDK and Freedom Studio. Freedom Studio is now, quite literally, an Eclipse front end to running Freedom-E-SDK projects and Makefiles.

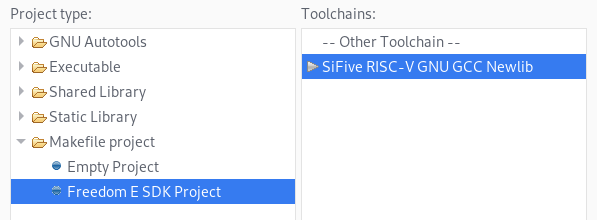

The new project dialog now has an option for a Freedom-E-SDK Project.

This project type allows you to select any of the targets supported by Freedom-E-SDK as well as any of the examples in Freedom-E-SDK. Note also that Freedom-E-SDK has BSPs for SiFive's RTL deliverables now allowing for Freedom-E-SDK examples to be run directly on our IP testbenches.

What is great about this integration between Freedom-E-SDK and Freedom Studio is that we have the ability to automatically generate Freedom Metal BSPs from SiFive Core Designer deliverables thereby allowing Freedom Studio (and Freedom-E-SDK) to target any IP delivered by SiFive. Please see the Application Note Custom Core Software Getting Started Guide for details on how to do this. We will continue to streamline this process in the near future.

Programming Arty Boards Directly from Freedom Studio

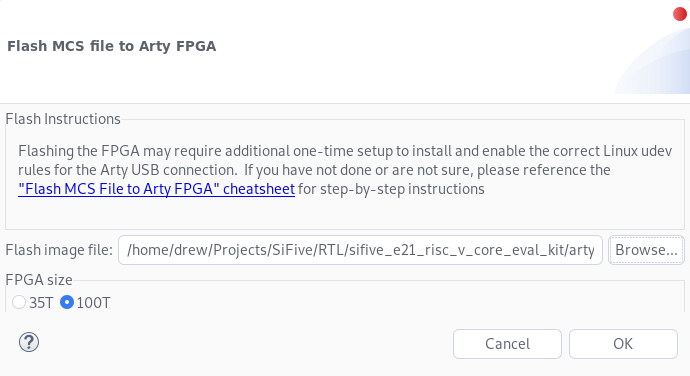

SiFive's Standard Cores and SiFive Core Designer deliverables include FPGA bitstreams which wrap our RISC-V Core IP deliverables with a peripheral sub-system, making it suitable for immediate software development. We currently target the Digilent Arty line of FPGAs due to their low-cost, capacity, and availability.

In order to streamline the process of evaluating SiFive IP, we now have the ability to program the Arty A7-35T and A7-100T boards directly from Freedom Studio greatly simplifying the evaluation process.

SEGGER JLINK Support Built In

SEGGER has been one of the earliest and strongest supporters of RISC-V in the tools ecosystem supporting SiFive devices as early as September 2017. When developing the newly launched HiFive1 Rev B we were excited about the possibility of adding a SEGGER JLINK probe directly on the board. This has several benefits including JLINK's legendary debug performance as well drag-and-drop programming capabilities. Freedom Studio has had built-in support for JLINK probes for some time, however, in order to make development on the HiFive1 Rev B as easy as possible, we now include SEGGER's JLINK debug software directly in Freedom Studio.

Available Today

Freedom Studio 2019.03 is available today for all 3 major Operating Systems at https://www.sifive.com/boards. Please visit our Forums and let us know what you think.